Железо - ALTERA: микросхемы программируемой логики (ознакомительный материальчик). Осваиваем программируемые логические матрицы фирмы – altera Установка драйвера

для программатора USB Blaster

Это первая часть цикла посвященная программируемой логике и среде разработки Quartus компании Altera. В ней разбирается процесс получения дистрибутива бесплатной редакции IDE Quartus. А также процесс создания нового проекта в данной среде.

Следующая часть цикла: ПЛИС Altera. Часть 2: проектирование цифровой схемы.

Во второй части разбирается процесс добавления к проекту новых файлов. Визуальное проектирование цифровой схемы.

Данный цикл статей ориентирован на работу с платой CTRL-CPLD-EPM570 на чипе Altera Max II. Эта плата не является строго необходимой для успешного освоения материала, так как описываемый в нем проект не использует каких-то специальных возможностей Max II.

Для загрузки проекта в микросхему используется недорогой программатор совместимый c Altera USB Blaster.

Шаг 1. Получение дистрибутива Altera Quartus

Внимание! В 2015 году Altera была приобретена компанией Intel. Бренд Altera прекратил существование в июле 2018 года, адрес сайта altera.com теперь никуда не ведет. Новое имя Altera – Intel Programmable Solutions Group (PSG). Вся документация и ПО необходимые для работы с ПЛИС Altera теперь доступны на сайте intel.com

Для создания проектов под ПЛИС Altera используется фирменная IDE - Quartus. Версий Quartus существует бесчисленное множество, и требуется выбрать правильную под имеющуюся микросхему. Altera регулярно выкидывает поддержку старых чипов из новых версий своего ПО. В свою очередь, в новых версиях Quartus меняются требования к программному и аппаратному обеспечению компьютера. Например, Quartus 13.1 является последней версией работающий как 64‑х так и 32‑х разрядных системах.

Данная серия статей ориентирована на Quartus версии 13.1. Так как с одной стороны, он не имеет специальных требований к разрядности операционной системы. С другой - он поддерживает микросхемы серии MAX II.

Для получения дистрибутива Quartus необходимо иметь аккаунт на сайте intel.com или intel.ru К сожалению, в настоящее время (в декабре 2018 года) процедура регистрации на сайте Intel несколько затруднена. Форму регистрации отыскать непросто. На нее можно выйти только на заключительном этапе загрузки дистрибутива. Также, в процессе регистрации Вам понадобится предоставить действующий адрес электронной почты, номер сотового телефона и обязательно придумать сложный пароль.

Пока идет активный процесс слияния Intel и Altera лучше воспользоваться сторонними ресурсами для загрузки Quartus. Дистрибутив выложен в общий доступ на Yandex‑диск, ссылка для загрузки: https://yadi.sk/d/bcrz7IAAKY6dQg

Для работы с микросхемой MAX II потребуется сам Quartus, и пакет для поддержки MAX II и MAX V. Это файлы «QuartusSetupWeb-13.1.0.162.exe » и «max_web-13.1.0.162.qdz » соответственно.

В конце статьи доступна и старая версия инструкции по загрузке дистрибутива: . По ней можно получить примерное представление о том, как загрузить дистрибутив с сайта intel, так как на сайте Intel используется Software Selector от Altera. И также как у Altera, Software Selector перенаправляет пользователя на страницу входа при попытке скачать любой файл, в случае если пользователь предварительно не зашел на сайт со своей учетной записью.

Данная страница входа - единственное место, которое содержит ссылку на форму регистрации на сайте Intel. Ссылки для регистрации располагаются в правой части страницы. Для рядовых пользователей можно использовать ссылку «Register now for an individual account ». Ссылка обозначена на рисунке ниже.

Шаг 2. Установка Quartus II Web Edition 13.1

Установка САПР Quartus II не таит каких‑либо сюрпризов и проходит по отработанному алгоритму «Next → Next → Finish».

Параметры установки изменять не требуется. В дальнейшем предполагается что Quartus II был установлен с параметрами по умолчанию.

По окончании установки среда Quartus запустится автоматически. Этот автозапуск активирован по умолчанию.

При первом запуске САПР Quartus будет предложено настроить отправку телеметрии в Altera (здесь это называется TalkBack) и выбрать тип лицензии.

Отключение или включение «TalkBack» задается галочкой «Enable sending TalkBack data to Altera», которая доступна и после установки Quartus через меню Tools → Options → Internet Connectivity → кнопка «TalkBack Options…».

При запросе типа лицензии необходимо просто выбрать второй пункт: «Run the Quartus II software». Таким образом Вы выберете бесплатную лицензию.

На этом установка и первичная настройка ПО завершена и можно переходить к созданию своего первого проекта.

Шаг 3. Quartus II — создание первого проекта

Первым делом создайте папку для нового проекта. Назовите ее «firstproject».

Внимание! Путь до директории проекта не должен включать кириллических символов! С поддержкой кириллицы у Quartus II 15 и 13 версии имеются проблемы. Другие версии не тестировались.

Теперь запустите Quartus II. При запуске свежеустановленного Quartus II Вас встретит окно, вид которого представлен ниже.

Для создания нового проекта воспользуйтесь мастером доступным по кнопке «New Project Wizard» или через меню File → New Project Wizard.

При запуске мастера будет выведено окно, в котором представлено краткое перечисление параметров проекта, настраиваемых в процессе работы мастера.

Нажмите «Next» и будет выполнен переход к окну представленном на скриншоте ниже. В этом окне необходимо указать рабочую директорию («What is the working directory for this project?») и название всего проекта в целом («What is the name of this project?»). А также имя его главного модуля («What is the name of the top-level design entity for this project? …»).

В качестве имени главного модуля мастер автоматически подставляет название проекта и это общая рекомендация для проектов в Quartus II, от которой не стоит отклоняться без реальной необходимости.

Пара слов о самом «главном модуле». Проект Quartus II может включать в себя множество файлов (модулей) описывающих различные функциональные блоки проектируемой интегральной схемы. И среди этого множества обязательно выделяется один файл, в котором описываются взаимосвязи между всеми блоками схемы - top‑level design entity. Для небольших проектов, содержащих всего один файл, этот единственный файл будет являться и главным модулем проекта.

На следующем шаге мастер предложит добавить в новый проект файлы из каких-либо ранее созданных проектов. Так как это первый Ваш проект, то просто перейдите к третьему шагу.

Третий шаг один из самых важных. Здесь необходимо указать конкретную модель используемой Вами микросхемы ПЛИС. Окно мастера на данном шаге представлено на скриншоте ниже. В этом окне доступно множество параметров для поэтапного отбора необходимой микросхемы из обширного списка доступных. Начать лучше всего с блока «Device Family». Здесь нужно выбрать семейство к которому относится Ваш чип. На плате CTRL-CPLD-EPM570 установлен чип EPM570T100C5N, который относится к семейству Max II.

В блоке справа – «Show in ‘Available devices’ list», можно настроить фильтр для сокращения перечня микросхем, который располагается в нижней части окна. Можно указать тип корпусировки микросхемы. Количество выводов ее корпуса. А также скорость работы ядра в условных единицах. Предпоследним идет фильтрация по названию микросхемы. Удобнее всего будет использовать именно её, так как название микросхемы уже точно известно. Но по маркировке EPM570T100C5N никаких микросхем к выбору не предлагается. Сократите название до EPM570T100C5, и выберите в появившемся списке микросхему с этим названием как ближайшую совместимую.

Если обратится к даташиту, то выяснится что последняя буква N в маркировке микросхемы обозначает лишь отсутствие свинца в упаковке чипа. Данный факт не имеет значения для Вашего проекта в Quartus II так как ядро у EPM570T100C5N и EPM570T100C5 абсолютно идентично.

Перейдите к следующему, четвертому шагу – «EDA Tool Settings». Здесь можно настроить интеграцию с различными средствами автоматизированного проектирования от сторонних разработчиков, которые используются профессиональными проектировщиками микросхем. Так как целью этой статьи является помощь в освоении САПР Quartus II, а не целого пакета приложений стоимостью многие тысячи долларов, то просто перейдите к заключительному шагу.

На последнем шаге выводится обобщенный список параметров Вашего нового проекта. Проверьте чтобы были верно заданы такие параметры как: имя и рабочая директория проекта, top-level design entity, маркировка используемой микросхемы. После чего нажмите кнопку «Finish». На этом все! Проект создан.

Возможно, Вы обратили внимание что кнопка «Finish» доступна для нажатия уже с первого шага мастера. И ее действительно можно нажать уже на первом шаге, задав только рабочую директорию, имя проекта и главного модуля. Только эта информация является абсолютно необходимой для создания нового проекта. Все остальные параметры доступны для настройки в любое время, из главного меню программы. Так, чтобы добавить еще файлов в свой проект (второй шаг мастера) используйте меню Project → Add/Remove Files in project. Для выбора или изменения модели микросхемы под которую создается проект (третий шаг мастера) используйте меню Assignments → Device. Интеграция с дополнительными инструментами разработки (предпоследний шаг мастера) – это Assignments → Settings → EDA Tool Settings.

Вообще, все настройки проекта собраны в окне, вид которого представлен на скриншоте ниже. Окно вызывается через меню Assignments → Settings.

Пункт Files – именно это окно вызывается и из главного меню программы (Project → Add/Remove Files in project). EDA Tool Settings – аналогично. Выбор микросхемы доступен по кнопке «Device…» в правом верхнем углу окна настроек проекта.

На этом первая часть статьи по обучению работе с ПЛИС компании Intel (Altera) завершается.

(Архив) Получение дистрибутива Altera Quartus

Для получения дистрибутива Quartus зайдите в свой аккаунт myAltera на сайте altera.com: кнопка «LOG IN» в правом верхнем углу сайта, рядом со строкой поиска.

Если у Вас еще нет аккаунта myAltera, то Вы можете создать его просто перейдя по ссылке в самом низу формы регистрации, строка «Don’t have an account? Create one».

После входа в myAltera перейдите в центр загрузки сайта . Ссылка на момент написания: https://www.altera.com/downloads/download-center.html

Если ссылка окажется нерабочей, то перейдите в центр загрузки через домашнюю страницу своего аккаунта . Для этого выберите раздел «SUPPORT » и в нем перейдите по ссылке «Downloads », которая и приведет Вас в центр загрузки.

В центре загрузки есть прямые ссылки на загрузку последней версии Quartus

в различных редакциях. Ниже располагается блок «Software Selector

», прокрутите страницу до него.

В центре загрузки есть прямые ссылки на загрузку последней версии Quartus

в различных редакциях. Ниже располагается блок «Software Selector

», прокрутите страницу до него.

В

Software Selector реализовано несколько способов выбора необходимо

го

дистрибутива Q

uartus, вкладки: «

Select by Version»

(прямой выбор по

требуемой

версии ПО

), «

Select by Device»

(выбор версии ПО по наличию поддержки конкретной микросхемы

), «

Select by Software» (выбор программного продукта

по

его названию

).

В

Software Selector реализовано несколько способов выбора необходимо

го

дистрибутива Q

uartus, вкладки: «

Select by Version»

(прямой выбор по

требуемой

версии ПО

), «

Select by Device»

(выбор версии ПО по наличию поддержки конкретной микросхемы

), «

Select by Software» (выбор программного продукта

по

его названию

).

Наиболее удобным вариантом представляется выбор по наличию поддержки имеющейся микросхемы.

Например, если используется микросхема Altera Max II , то необходимо выбрать вкладку « Select by Device», и в блоке « Devices» раскрыть пункт « MAX series». В появившемся списке выбрать Max II .

Справа от блока Devices будет выведен

список редакций и версий Quartus

включающих поддержку Max II

.

Бесплатной редакцией является только Web Edition.

Справа от блока Devices будет выведен

список редакций и версий Quartus

включающих поддержку Max II

.

Бесплатной редакцией является только Web Edition.

При выборе версии обратите внимание на тот факт, что Quartus II начиная с версии 14.0 работает только в 64‑битных системах. По этой причине рекомендую остановится на Quartus II 13.1. Далее будет описана работа и процесс установки именно для тринадцатой версии.

После выбора версии Вы перейдете на страницу параметров загрузки дистрибутива Quartus II Web Edition.

«Operating System» - Windows.

« Download Method » выбирайте по своему усмотрению. Отличие «Akamai DLM3 Download Manager» от « Di rect Download» в том, что в первом случае перед загрузкой файлов самого Quartus нужно будет сначала загрузить и запустить дополнительное приложение под ОС Windows. Это приложение позволяет выбрать к загрузке одновременно несколько файлов, а также поддерживает их докачку. При выборе режима загрузки « Di rect Download» файлы можно будет загружать отдельно, каждый по своей ссылке, силами Web-браузера.

На скриншоте выше выбран вариант загрузки « Di rect Download» .

Загрузите файлы «Quartus II Software » и «MAX II, MAX V device support ». Это необходимый минимум для работы с микросхемой MAX II .

Ты ждал знак? Вот он!

Много лет я не решался начать программировать ПЛИС, потому что это сложно, дорого и больно (как мне казалось). Но хорошо, когда есть друзья, которые помогают сделать первый шаг. И теперь я не понимаю одного - ПОЧЕМУ Я ЖДАЛ ТАК ДОЛГО?

Сейчас я помогу сделать первый шаг и тебе!

А зачем оно мне?

Ты устал постоянно читать доки по своему МК или держать кучу информации в голове. Ты все переписал на asm, но скорости все равно не хватает. Ты подключил два внешних устройства к своему МК, подключаешь третье, но у тебя кончились прерывания, перестают работать те модули, что уже работали. Ты берешь другой МК, более мощный из той же линейки, но опять мануалы, регистры флагов, биты… ад. Меняешь платформу: переходишь на другой МК и выкидываешь на помойку свои знания по прежней платформе. Что бы ты не делал - оно дается тяжело. Ты находишь популярную платформу, в которой можно легко из компонентов собирать проект, но выше аппаратных ограничений данного МК все равно не удается прыгнуть… Где-то на краешке сознания иногда проскакивает мысль, что вот на ПЛИС это бы точно заработало быстро и параллельно, что это «именно та задача, которую бы надо решать на плис», но я стар/глуп/занят/etc чтобы суметь/начать такое делать.

Хочешь наконец вздохнуть свободно? Идем дальше!

Радость от разработки на ПЛИС

У меня был тяжелый рабочий день. С одной работы я приехал на вторую работу, потом на дачу, вечером домашние дела, уроки, потом семейный просмотр кино и только в 23 часа я оказался совершенно свободен! Сказать, что я был уставший - ничего не сказать. Но в таком состоянии я сел за ноут с твердой целью: сделать генератор меандра на 440 Гц. Прошло 20 минут и я уже слышал его в наушниках. Я не верил своим ушам! Еще 15 минут мне потребовалось, чтобы сделать ШИМ и менять громкость. К тому времени плата с ПЛИС у меня была всего с неделю и до этого я пролистал всего пару книг по Verilog.В тот вечер я понял: ВОТ ОНО! Вот та платформа, в которой я быстро и легко могу превращать свои мысли в реально работающее железо!

Почему так?

Опишу плюсы, которые есть в изучении и применении ПЛИС, хотя их и так все знают:- Универсальность знаний - при смене модели МК нужно читать доки. При смене производителя МК нужно читать доки. Нужно постоянно читать доки, постоянно держать в голове кучу информации. При разработке на ПЛИС, если знаешь Verilog или VHDL, то можно не только программировать любой ПЛИС из линейки одного производителя, но и при желании перейти на другого (Altera, Xilinx). Хоть и будут моменты с освоением другой среды разработки, тонких аппаратных моментов, но сама суть подхода проектирования устройств на HDL от этого не изменится.

- От идеи к железу - при разработке проекта, если тебе не хватает одного мк, то приходится выбирать другой. В принципе можно строить предположения справится или не справится этот МК с проектом. Либо есть какой-то конкретный МК и ты пытаешься туда вместить проект. Чаще всего именно так. Мне это чем-то напоминает подход моего деда, который делает лестницу из того, что есть в сарайке. Хотя можно спроектировать лестницу, купить досок, которые подойдут… От идеи к железу, а не наоборот.

- Простота применения чужих разработок - можно взять чужой модуль и применить его в своем проекте. По коду сможете понять, как он работает. Даже, если он для xilinx, а вы делаете под altera. Иногда это получается не сарзу, но это проще, чем, например, добавлять двоичные библиотеки к проекту на c++/Qt

- Независимость блоков. Блоки в HDL, как чистые фунции в ЯП. Зависят только от входных сигналов. Разработанный и отлаженный модуль в будет и дальше работать правильно, как бы не рос проект. Ничто снаружи не повлияет на правильность его работы изнутри. Да и вообще можно забыть, как он работает - это черный ящик. К тому же, блоки работают параллельно .

Проблема выбора

Сильно останавливают вопросы, что выбрать: Altera/Xilinx, Verilog/VHDL, какую отладочную плату взять. Но обо всем по порядку.Производитель

Я выбрал Altera . Почему? Ну мы вот так с другом решили, хотя название Xilinx мне красивее. НО. Если ты сейчас не можешь выбрать, то я сделаю это за тебя. Тебе нужен Altera! Почему? Я не знаю. Сейчас важнее сделать шаг: сделать выбор. Я выбрал Altera и пока не пожалел.

Язык

Берем Verilog - потомучто … ну ты понял.

Отладочная плата

На выбор отладочной платы ушло больше всего времени. Понятно, что платы отличаются установленной микросхемой ПЛИС. А микросхемы ПЛИС отличаются друг от друга количеством элементов. Но совершенно не понятно, сколько их потребуется для твоих тестовых проектов. Поэтому большую часть времени я потратил на поиск всевозможных проектов на ПЛИС на предмет того, чтобы узнать, сколько они потребляют ресурсов ПЛИС.В семействе Altera, за разумные деньги мы можем купить платы с CPLD MAX II на 240, 570 и 1270 элементов, либо более старшие микросхемы FPGA, которые Cyclone 1, 2, 3, 4 с количеством до 10000 и более ячеек. Как же выбрать?

Даже на базе 240 ячеек, проект Марсоход делает просто огромное количество проектов . Настоятельно рекомендую ознакомиться, чтобы иметь примерное представление о сложности проектов, которые можно уместить в 240 ячеек. С другой стороны, существуют проекты , которые полностью программируются под аппаратную копию определенного ПК, включая процессор и всю логику вокруг него (NES , Speccy , Orion , ЮТ-88 , etc). Для этого уже требуется пять, десять и более тысяч ячеек. Плюс эти платы содержат дополнительные внешние устройства.

Поэтому я бы посоветовать взять что-то среднее между 240 и 10000 ячейками, с предпочтением в сторону увеличения в зависимости от доступных средств. На отладочной плате лишние ячейки это не страшно, а если их не хватит - уже ничего не поделаешь. Потом, когда устройство отлажено, станет ясно, сколько надо ячеек, купить под нужное количество, без лишнего «обвеса», дешевле и оставить в готовом устройстве.

То, чем действительно отличаются MAX от Cyclone"ов, кроме количества ячеек, это:

1) У серии MAX внутри нет PLL. На каждой отладочной плате есть генератор, как правило на 50 МГц. Основной массе проектов этого будет достаточно. Все синхронизации будут происходить путем деления 50 МГц на какое-нибудь значение. Либо, можно взять внешний генератор и подать на отдельный вход ПЛИС. А что, если потребуется частота выше 50 МГц? Мне не удалось с ходу найти генераторы выше 50 МГц. Но тут как раз на помощь и приходит PLL, который встроен в Циклоны. На нем можно умножить частоту, например, до 100 МГц.

2) В серии Cyclone встроены аппаратные блоки умножения. Их количество зависит от конкретной модели - тут как раз можно «всетаки заглянуть в инструкции», чтобы узнать сколько. Если предполагаете делать какой-то ЦОС, то они пригодятся: сэкономят ячейки, увеличат скорость. С другой стороны, если нет умножителей, их можно синтезировать, но у маленькой ПЛИС на это может не хватить ресурсов.

Во всем остальном у меня критерий «влезло/не влезло». Отладка на заведомо бОльшей, чем нужно плате, с последующей заливкой в минимально необходимую для этого.

Сколько нужно денег?

Программатор

Я считаю, что у меня нет времени, чтобы паять программаторы на рассыпухе.

300 рублей. Я свой брал на ебее , выглядит так:

Отладочная плата

Выбор широкий, в зависимости от количества денег.

Начальный уровень

350 - 550 рублей. Это платы на MAX II ( или ячеек). Могут подойти для начального ознакомления и дальнейшего пристройства в конечные устройства. На плате есть генератор, пара кнопок, пара светодиодов, остальные 80 выводов на свое усмотрение.

Блок питания

Обязательно должен быть, но не всегда идет в комплекте. Потребуется БП на 5 вольт и ток 2А.

Средний уровень

от 900 до 1500 рублей. Это платы Cyclone 1, 2, 3, 4 отличающиеся в основном количеством ячеек.

Маркируются примерно так:

EP2

C5

T144 - Cyclone 2 примерно 5к ячеек

EP4

CE6

E22C8N - Cyclone 4 примерно 6к ячеек

EP2

C8

Q208C8N - Cyclone 2 примерно 8к ячеек

Можно заметить, что Cyclone 3 может иметь больше ячеек, чем Cyclone 4.

Вот несколько вариантов:

835 рублей.

ALTERA FPGA CycloneII EP2C5T144 Minimum System Board for Learn good

880 рублей

Altera CycloneII EP2C5T144 FPGA Mini Development Learn Core Board E081

1265 рублей

EP2C8 EP2C8Q208C8N ALTERA Cyclone II FPGA Evaluation Development Core Board

Платы с расширенными возможностями . Это платы, на которых установлены дополнительные модули (UTP, USB, AUDIO), разъемы (SD, VGA), кнопки, переключатели, светодиоды, семисегментные индикаторы и т.д. Либо может идти базовая плата, а к ней могут прилагаться платы расширения отдельно.

У меня трудится такой комплект - плата + плата расширения:

Altrea EP4CE10E22 FPGA CORE Board+ Device Board USB/Sound/Ethernet/SD Card/VGA

2760 рублей

Вот основная плата. На ней есть 2 светодиода, 2 кнопки, 4 переключателя, семисегментный интикатор и микросхема оперативной памяти.

Плата расширения. На ней распаяны SD, VGA, а так же контроллеры USB(High Speed USB2.0 Chip: CY7C68013A), AUDIO(Sound Card up to 96kHz/32bit ADC/DAC: WM8731S), UTP(100M Ethernet interface: DM9000A):

Эти платы просто вставляются одна в другую, но у меня она пока лежит в ящике. Для своих поделок у меня макетка, с которой я соединяюсь шлейфом, который идет в комплекте. Еще в комплекте идет блок питания на 5 вольт.

Для большинства радиолюбителей конструкторов занимающихся собственными разработками давно известны и освоены цифровые микросхемы. Многие достаточно давно проектируют свои конструкции на микроконтроллерах так как это в значительной степени уменьшает габариты и улучшает функциональность устройств. Вот только беда в том, что не всё можно построить на основе контроллера. Быстродействующие устройства требующие мгновенной реакции на изменяющиеся входные сигналы построить на микроконтроллере не удастся так как в нём организована поэтапная (конвейерная) обработка команд в результате которых принимается решение о выдаче того или иного сигнала. Поэтому наряду с микроконтроллерами приходится использовать обычную логику, иногда с приличным количеством корпусов. Следствием этого является большое число внешних соединений, сложность конструкции и большие габариты печатных плат, большая длина соединительных проводников, сложность построения устройств с высокой тактовой частотой, низкая надёжность. Решением данной проблемы является использование программируемых логических интегральных схем (ПЛИС), которые представляют собой совокупность некоторого числа функциональных базовых элементов, не имеющих жестких электрических соединений между собой, что позволяет задавать практически произвольную конфигурацию с целью создания той или иной электронной схемы. На первом этапе ПЛИС представляли собой микросхемы с пережигаемыми перемычками такие как К556РТ4-РТ5 и др. на них можно было создать некоторые функции но запихнуть небольшую схему со счётчиками и триггерами было не возможно.

Этапы проектирования устройств на основе простой логики плохо автоматизированы и в случае ошибки необходимо дорабатывать плату вводить дополнительные элементы. Изучение программного Пакета MAX+plus II BASELINE и ПЛИС фирмы Altera, позволит не только упростить схему но и не наступать на множество подводных камней. Данное программное обеспечение можно использовать и при проектировании схем на 155серии и её аналогах. Для программирования (создания соединений) в PLD (а также и

CPLD) используются технологии EPROM, EEPROM и FLASH. Для радиолюбителей наибольший интерес представляют микросхемы FLASH так как они позволяют перепрограммировать кристалл порядка 100 раз и после снятия питающего напряжения сохраняют структуру установленную в результате программирования.

В данной статье будут рассмотрены вопросы поэтапной разработки схем на основе ПЛИС фирмы Altera — EPM3064А как наиболее дешёвой. Она размещена в 44 выводном корпусе типа PLCC. Микросхема имеет смешанное питание и мультивольтовый интерфейс ввода/вывода (I/O). Напряжение питания логического ядра 3,3 вольта элементов ввода/вывода – 5; 3,3; и 2,5 вольта. Максимальная тактовая частота 227,3мГц в зависимости от модификации. Установкой битов конфигурации возможно управлять крутизной фронтов (Slew Rate ) входных/выходных сигналов. Имеется также реализация выходов с открытым стоком установкой бита (Open Drain ). Имеется возможность установить режим энергосбережения который уменьшает более чем на 50% потребляемую мощность. Имеется также возможность установить бит секретности (security bit ) который не позволит скопировать внутреннюю конфигурацию микросхемы. Данная микросхема имеет 4 блока логических матриц и 64 макроячейки. Программируемые триггеры макроячеек имеют индивидуальные входы синхронизации (clock ), разрешения синхронизации (clock enable ), обнуления (clear ), и предустановки (preset ). Каждая макроячейка может рассматриваться как программируемая матрица И и фиксированная матрица ИЛИ . На выходе матрицы ИЛИ включен регистр с конфигурируемой схемой управления. Схема управления регистром обеспечивает независимо программируемые сигналы синхронизации, разрешения синхронизации, обнуления, и предустановки. В данную микросхему по мнению автора можно запихнуть 10-15 корпусов 155 серии (в продаже имеются микросхемы EPM3256 с 16 блоками логических матриц и 158 выводами).

Архитектура EPM3064A включает следующие элементы: Логические блоки (LABs ). Макроячейки (Macrocells ). Логические расширители, разделяемый (Shareable ) и параллельный (Parallel ). Программируемая матрица соединений (PIA ). Блоки управления вводом/выводом (I/ O control blocks ). Микросхема имеет четыре специализированных входа (dedicated pin ) которые могут использоваться как входы общего назначения или входы высокоскоростных глобальных управляющих сигналов (синхронизации –clock , обнуления clear и двух сигналов разрешения выхода — enable ), для каждой макроячейки и контакта ввода вывода. Блок схема изображена на рис1.

РИС 1

РИС 1

Основу архитектуры EPM 3064A составляют логические блоки , состоящие из 16 макроячеек . Логические блоки соединяются вместе при помощи программируемой матрицы соединений (PIA ). К каждому логическому блоку подводятся следующие сигналы: 36 сигналов от PIA , используемых в качестве логических входов. Глобальные управляющие сигналы. Непосредственные цепи от входных буферов к регистрам, обеспечивающие высокое быстродействие. Подробнее о функциональном составе и принципе работы микросхемы можно почитать в .

РИС 2

РИС 2

Для программирования микросхемы необходимо изготовить специальный загрузочный кабель ByteBlasterMV Рис2 . Он позволяет быстро и эффективно изменять конфигурацию ПЛИС как в стадии тестирования проекта, так и во время эксплуатации. Перепрограммирование может быть выполнено непосредственно в системе. Пока идет программирование, выводы микросхемы переводятся в третье состояние, для избежания конфликта с системой. Сопротивление внутренних “подтягивающих” резисторов 50 кОм.

Данный загрузочный кабель можно использовать для программирования микросхем серий МАХ 3000А, МАХ7000, МАХ 9000 а так же многих других, подробнее можно почитать в . Схема загрузочного кабеля приведена на рис3. Разъём Х1 подключается непосредственно к параллельному порту компьютера или через удлиняющий кабель причём его длинна не должна превышать 1,5 метра. Питание для программатора берётся непосредственно от схемы проектируемого устройства. Для нормальной работы программатора необходимо установить драйвер ByteBlasterMV о чём будет описано далее. Микросхему D 1 желательно использовать оригинальную так как она может работать в диапазоне питающих напряжений от 2,5 до 5 вольт (в крайнем случае можно заменить на 1564АП5). Все резисторы типа МЛТ 0,125. Конденсатор С1 керамический.

РИС 3

РИС 3

Печатная плата Рис4 . изготовлена из одностороннего фольгированного стеклотекстолита толщиной 1,5мм и размерами 52х43мм.

РИС 4

РИС 4

Для создания проекта в среде системы MAX+PLUS II фирмы ALTERA необходимо скачать с интернета и установить Рис5. свободно распространяемый файл baseline10_1.exe ссылка на сайт приведена в . После установки программы для полнофункциональной работы необходимо зайти на сайт фирмы Альтера и получить файл лицензии . На этойстранице выбираете ссылку MAX+PLUS II software for students & universities . На следующей странице выбираете ссылку Version 10.2, 10.1, or 9.23 и нажимаете кнопку continue . На следующей странице в окне набираете Ваш регистрационный номер жесткого диска. Для этого в Windows нажимаете кнопку ПУСК затем Программы, Стандартные, командная строка, и набираете команду dir иenter .

РИС 5

РИС 5

Во второй строке распечатается серийный номер диска состоящий из 8 цифр. Вот его и необходимо ввести. Далее нажимаете кнопку continue и на следующей странице заполняете форму. По окончании заполнения формы нажмите кнопку continue. Файл лицензии будет выслан вам по почте. Создайте папку c:\mp2student\ и поместите туда высланный вам файл license.dat . Для установки файла лицензии запустите MAX+plus II 10.1 BASELINE далее нажмите вкладку Options и License Setup в появившемся окне нажмите кнопку Browse, и укажите путь до файла лицензии. Нажмите кнопку OK . После этого все приложения станут доступные. После этого необходимо установить файл драйвера программатора. Для этого нажимаем кнопку ПУСК затем Настройка, панель управления, установка оборудования далее затем кнопку Д а, устройство уже подсоединено и кнопку далее . В следующем окне выбираем Добавление нового устройства и Д алее . Устанавливаем кнопку на Установка оборудования выбранного из списка вручную и Д алее . В списке выбираем Звуковые, видео и игровые устройства и Д алее . Нажимаем кнопку У становить с диска , далее кнопку Обзор . Устанавливаем путь C:\maxplus2\Drivers\win2000 если у вас установлен WindowsXP затем кнопку ОК. Из списка выбираем Altera ByteBlaster , кнопку далее и Готово .

Система MAX+PLUS II имеет средства удобного ввода проекта, компиляции и отладки, а также непосредственного программирования устройств. Программное обеспечение системы MAX+PLUS II содержит 11 приложений и главную управляющую программу. Различные приложения, обеспечивающие создание проекта, могут быть активизированы мгновенно, что позволяет пользователю переключаться между ними щелчком мыши или с помощью команд меню. В это же время может работать одно из фоновых приложений, например, компилятор, симулятор, анализатор синхронизации и программатор.

В таблице приведено описание приложений.

Таблица

| Приложение | Выполняемая функция |

| Hierarchy Display | Обзор иерархии — отображает текущую иерархичнскую структуру файлов в виде дерева с ветвями, представляющими собой подпроекты. |

| Graphic Editor | Графический редактор — позволяет разрабатывать схемный логический проект в формате реального отображения на экране. |

| Symbol Editor | Символьный редактор — позволяет редактировать существующие символы и создавать новые. |

| Text Editor | Текстовый редактор — позволяет создавать и редактировать текстовые файлы логического дизайна, написанные на языках AHDL, VHDL, Verilog HDL. |

| Waveform Editor | Сигнальный редактор — выполняет двойную функцию: инструмент для разработки дизайна и инструмент для ввода тестовых векторов и наблюдения результатов тестирования. |

| Floorplan Editor | Поуровневый планировщик — позволяет графическими средствами делать назначения контактам устройства и ресурсов логических элементов. |

| Compiler | Компилятор — обрабатывает графические проекты. |

| Simulator | Симулятор — позволяет тестировать логические операции и внутреннюю синхронизацию проектируемой логической цепи. |

| Timing Analyzer | Временной анализатор — анализирует работу проектируемой логической цепи после того, как она была синтезирована и оптимизирована компилятором. |

| Programmer | Программатор — позволяет программировать, конфигурировать, проводить верификацию и тестировать ПЛИС фирмы ALTERA. |

| Message Processor | Генератор сообщений — выдает на экран сообщения об ошибках, предупреждающие и информационные сообщения. |

Создадим рабочий каталог в котором будем размещать наш проект C:\ALTERA_WORK\schetchic . Схему можно описывать на языках AHDL, VHDL, Verilog HDL (для тех кто предпочитает программирование) или графическим способом (больше подходит для радиолюбителей). Файл проекта - это графический, текстовый или сигнальный файл, созданный с помощью графического или сигнального редакторов системы MAX+PLUS II. Этот файл содержит логику для проекта MAX+PLUS II и компилируется компилятором. Компилятор может автоматически обрабатывать следующие файлы проекта: графические файлы проекта (.gdf ); текстовые файлы проекта на языке AHDL (.tdf ); сигнальные файлы проекта (.wdf ); файлы проекта на языке VHDL (.vhd ); файлы проекта на языке Verilog (.v ); схемные файлы OrCAD (.sch ); входные файлы EDIF (edf ); файлы формата Xilinx Netlist (.xnf ); файлы проекта Altera (.adf ); файлы цифрового автомата (.smf ). Вспомогательные файлы - это файлы, связанные с проектом MAX+PLUS II, но не являющиеся частью его иерархического дерева. Большинство таких файлов не содержит логики проекта. Некоторые из них создаются автоматически приложением системы MAX+PLUS II, другие - пользователем. Примерами вспомогательных файлов являются файлы назначений и конфигурации (.acf ), символьные файлы (.sym ), файлы отчета (.rpt ) и файлы тестовых векторов (.vec ).

Итак в главном меню нажимаем File затем New и выбираем пункт Graphic Editor file и OK рис6. Откроется окно графического редактора. Далее сохраним наш проект под именем schetchic . gdf в наш каталог C:\ALTERA_WORK\ для этого нажимаем File затем Save As и OK . Привяжем имя файла к файлу проекта для этого в главном меню нажимаем File затем Project и далее Set Project to Current File или вместо этого можно нажать одновременно клавиши Ctrl + Shift + J . Зададим тип микросхемы который будет использоваться в проекте. Для этого в главном меню нажмем кнопку Assign затем Device .

В появившемся окне в строке Device Familay выбираем серию MAX 3000 A . А в окне Devices EPM3064ALC44-4 и OK . Если вы не знаете какой объём у вас будет занимать проект то Devices лучше установить AUTO , компилятор сам подберёт тип микросхемы.

РИС 6

РИС 6

В рабочей библиотеке имеются элементы различного вида:

1). Логических примитивов (находящихся в папке c:\maxplus2\max2lib\prim\) таких элементов как and , or , nor и др. с различным количеством входов.

2). Аналогов дискретной логики 74-й серии являющиеся аналогами 155 серии (находящихся в папке c:\maxplus2\max2lib\mf\).

3). Параметризированных логических функций, позволяющих создавать проекты цифровых устройств любой сложности (находящихся в папке c:\maxplus2\max2lib\mega_lpm\).

Cоздадим каталог в котором будем размещать собственную библиотеку компонентов C:\ALTERA_WORK\Altera_Lib и подключим её к проекту. Для этого в главном меню нажмем кнопку Options затем User Libraries и в окно Directory Name введём путь c:\altera_work\altera_lib затем OK. Разместить на экране символ можно двумя способами для этого щелкнем правой кнопкой по месту где хотим разместить элемент и выберем в появившемся окне менюшку Enter Symbo l в окне Symbol Name появившегося окна набрать имя элемента и нажать ОК . Или выбрать необходимую библиотеку в окне Symbol Libraries диалогового окна Enter Symbol и двойным щелчком левой клавиши мыши открыть её. Затем аналогичным образом выбрать необходимый элемент в окне Symbol File . Если проект небольшой и вас устраивают все элементы находящиеся в библиотеке то таким образом устанавливаем все необходимые элементы и соединяем их выводы при помощи проводников. Для этого в графическом редакторе слева находятся пиктограммы при нажатии на которые можно получить соединение прямая линия, линии размещённые под прямым углом, сектора и окружности.Если линия выделена красным цветом то на ней можно нанести адрес соединения а само соединение не делать. Входные и выходные цепи наносят выбрав в библиотеке элементов input и output (при необходимости присваиваем им имя). Для нанесения логической единицы и нуля набираем vcc или gnd . А если необходим свой символ то необходимо открыть новое окно графического редактора и нарисовать схему компонента Рис7 присвоить ему имя и сохранить в библиотеке c:\altera_work\altera_lib . Привязать к файлу проекта и откомпилировать нажав ctrl+ L . Если ошибок нет, то можно проверить работу схемы при помощи симулятора.

РИС 7

РИС 7

Для этого открываем Waveform Editor , сохраняем файл под тем же именем. На первой строчке под Name : щёлкаем правой кнопкой мышки, и выбираем меню Enter nodes from SNF , в появившемся окне нажимаем кнопку List , в окне Available Nodes & Groups появятся все входы и выходы нашей схемы. Выделяем необходимые (в данном случае IN и OUT ) и нажимаем кнопку => выделенные символы скопируются в правое окно. Нажимаем OK . В редакторе можно увидеть осциллограмму Рис8. Под именем Value можно установить первоначальное состояние входного сигнала для этого левой кнопкой мышки щелкаем по строке слева, в редакторе высвечиваются пиктограммы логической 1 и 0, нажатием пиктограммы присваиваем состояние входа. Можно ввести изменяющийся во времени сигнал или Z состояние. Конечное время осциллограммы можно ввести зайдя в меню File затемEnd Time . Метки времени устанавливаются через меню Options затем Grig Size .

Для просмотра состояния осциллограммы во времени, запустим Simulator нажав кнопки Ctrl+ Shift+ L . Осциллограмму можно увидеть на Рис9. Если полученная модель компонента нас устраивает нарисуем изображение символа. Для этого откроем редактор символа, в главном меню нажимаем File затем New и выбираем пункт Symbol Editor file и OK рис6. Нажав левую кнопку мышки рисуем очертание символа предварительно выбрав слева в пиктограмме инструмент для рисования.

Двойным щелчком левой кнопки мышки открываем меню Enter Pinstub слева в окне указываем тип вывода вход иливыход I / O Type . В окне Full Pinstub Name Указываем имя вывода (в нашем случае IN — входOUT — выход). Размеры всех линий и надписей можно изменять и перемещать щёлкнув левой кнопкой по перемещаемому элементу. Файл необходимо сохранить под тем же именем что и файл графического редактора в нашу папку библиотеки.

Закрыв все вспомогательные окна можно ввести символ в файл нашего проекта.

Рассмотрим практическую схему трёхразрядного счётчика с динамической индикацией Рис10. Блок питания собран на микросхеме D 2 типа LM 317 и обеспечивает необходимое для D 1 напряжение.

РИС 10

РИС 10

Выходной ток разрядов индикатора может быть порядка 80 ма при всех включенных индикаторах, поэтому разряды индикаторов коммутируются транзисторами VT 1-VT 3. Для экспериментальной модели выбрана схема внутреннего генератора, внешние цепи которого представляют собой резисторы R 16,R 18,C 2, но в рабочей схеме генератор лучше делать внешним. По мнению автора ПЛИС не очень хорошо работают с ёмкостными нагрузками. Разъём Х1 необходим для подключения к программатору.

Рассмотрим внутреннюю структуру проекта Рис11. Все компоненты создавались заново, по приведённой выше методике и сохранялись в собственной библиотеке компонентов.

РИС 11

РИС 11

На схеме компонент 0_3r_commutator – это трёхразрядный коммутатор который переключает по очереди разряды индикатора а также выдаёт управляющие уровни на мультиплексоры 0_3 and _ or . Мультиплексоры подключают в зависимости от индицируемого разряда десятичные счётчики 0_2 b _10 d _ counter к двоично — семисегментному дешифратору 0_ bcd _7 seg . В названиях компонентов присутствует предлог 0 _ которым мы обозначаем элемент собственной библиотеки. На схеме в проекте MAX+PLUS II двойным щелчком левой кнопки мышки по компоненту откроется графический редактор и мы увидим схему элемента. На рис 12 изображен коммутатор,схема которого состоит из примитивов стандартной библиотеки. Название NOT – означает инвертор, DFF – D триггер,AND 2 – элемент И с двумя входами. На рис 13 приведена внутренняя схема двоично десятичного счётчика. На рис 14 мультиплексора. И рис 15 двоично — семисегментного дешифратора. Ниже приведен список некоторых мегафункций стандартной библиотеки.

РИС 12

РИС 12

РИС 13

РИС 13

РИС 14

РИС 14

Логические элементы (Gates):

lpm_and – элемент И

lpm_inv – элемент НЕ (инвертор)

lpm_bustri – шина с тремя состояниями

lpm_mux — мультиплексор

lpm_clshift — логический сдвиг

lpm_or – элемент ИЛИ

lpm_constant — константа

lpm_xor – Элемент исключающее ИЛИ

lpm_decode — декодер

mux – мультиплексор

busmux — мультиплексор

РИС 15

РИС 15

Арифметические компоненты:

divide* — делитель

lpm_compare — компаратор

lpm_abs – абсолютное значение

lpm_counter — счетчик

lpm_add_sub – сумматор/вычитатель

lpm_divide — делитель

lpm_mult — умножитель

Элементы памяти:

altdpram* — двухпортовое ОЗУ

lpm_latch – регистр-защелка

lpm_shiftreg – сдвиговый регистр

dcfifo* — Dual-Clock FIFO

lpm_ram_dp — двухпортовое ОЗУ

scfifo* — Single-Clock FIFO

lpm_ram_dq – ОЗУ с раздельным входным и выходным портом

csdpram — Cycle-Shared Dual-Port

lpm_ram_io — ОЗУ с общим входным и выходным портом

lpm_ff — Триггер

lpm_rom — ПЗУ

lpm_fifo — Single-Clock FIFO

lpm_dff* — D – триггер и сдвиговый регистр

lpm_fifo_dc — Dual-Clock FIFO

lpm_tff* – T -триггер

Другие функции:

clklock — PLL (Phase-Locked Loop)

pll – детектор фронта импульса

ntsc – генератор видеосигнала NTSC

После того как созданы все компоненты, нарисована общая схема проекта и сделаны все соединения, необходимо сохранить проект и произвести компиляцию. При отсутствии ошибок необходимо зайти в Waveform Editor и как было рассмотрено выше убедиться в правильности работы проекта Рис16.

РИС 16

РИС 16

Разведённая компилятором схема автоматически назначает входные и выходные ножки это можно посмотреть в Floorplan Editor нажав кнопку . В этом же редакторе можно изменить назначение ножек по собственному желанию. Для этого надо нажать кнопку и мышью перетащить имена выводов, отображаемых в окне Unassigned Nodes & Pins , на соответствующие номера выводов ПЛИС, а затем перекомпилировать проект. После этого любые изменения, вносимые во внутреннюю структуру проекта, т.е. не связанные с добавлением или удалением выводов, не будут изменять назначение выводов.

После этого подключаем схему Рис10 через разъём Х1 к программатору, а программатор к компьютеру(все эти процедуры проделываем при выключенном компьютере) подаём питание на схему. Открываем окно Programmer и нажимаем кнопку Program . После того как программа зальётся схема переключится в рабочий режим. Данный способ позволяет менять внутреннюю схему устройства в зависимости от изменяющихся задач не переделывая печатной платы.

Не смотря на кажущуюся сложность изучения программной среды MAX+PLUS II вы сможете делать проекты гораздо быстрее так как проектирование и отладка на компьютере даёт больше информации чем изготовление схемы на макетке и дальнейшее исследование при помощи осциллографа. Как уже отмечалось ранее полученные результаты можно с успехом использовать при изготовлении конструкций на основе 155-555 серии.

1 Назначение выводов в проекте Quartus II

В меню Assignements Device… выбираем ПЛИС, в которую вы собираетесь «залить» проект. В группе Device Family нужно выбрать семейство, к которому относится ваша ПЛИС. В поле Available devices выберите модель вашей ПЛИС. У меня, например, это Cyclone II, модель EP2C5T144C8.

В группе Show in "Available devices" list можно отсортировать устройства по типу корпуса (Package ) или по количеству выводов (Pin count ), чтобы быстрее найти вашу модель ПЛИС.

Нелишним будет задать, в каком состоянии будут находиться неподключённые ножки ПЛИС. Нажмите кнопку Device and Pin Options… , перейдите к пункту Unused Pins , и укажите состояние выводов.

После того как указали модель ПЛИС, закрываем окно Device , нажав кнопку OK .

Если вы хотите, чтобы синтезатор сам назначил функции выводам, то можно ничего больше не делать. А для того, чтобы вручную назначить выводы ПЛИС, идём в меню Assignements Pin Planner или нажимаем сочетание клавиш Ctrl+Shift+N .

Запуск инструмента назначения выводов Pin Planner

Запуск инструмента назначения выводов Pin Planner

Запустится инструмент назначения выводов Pin Planner . Внизу отображается список используемых в вашем проекте пинов ввода-вывода с соответствующими именами Node Name .

Теперь в столбце Location нужно задать номера выводов. Дважды кликаем на соответствующей ячейке и выбираем номер вывода, или же вводим с клавиатуры номер. Номера выводов будут зависеть от вашей макетной платы. Например, в моей плате тактовый импульс CLK, согласно мануалу, на 17 выводе, а выходам OUT1…OUT5 я назначу свободные выводы 94, 97, 100, 103 и 93.

После того, как все выводы были определены, окно планировщика пинов Pin Planner можно закрыть. Теперь скомпилируйте проект: Processing Start Compilation или Ctrl+L .

2 Установка драйвера для программатора USB Blaster

Подключим программатор USB Blaster к компьютеру (если у вас его нет, то можно приобрести на Али-Экспресс). При первом подключении необходимо установить драйвер. Он устанавливается стандартным образом, и находится в директории Квартуса, в папке drivers : C:\altera\13.0sp1\quartus\drivers

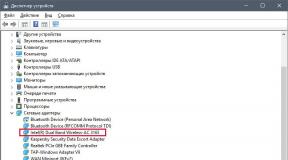

После установки драйвера, программатор будет отображаться в диспетчере устройств как Altera USB-Blaster.

через интерфейс JTAGПЛИС фирмы Altera поддерживают несколько режимов программирования. Сначала рассмотрим загрузку прошивки в ПЛИС через интерфейс JTAG . Подключите программатор к разъёму JTAG на плате с ПЛИС.

Запустим инструмент для программирования: Tools Programmer .

Добавим программатор. Для этого нажмём кнопку Hardware Setup… и в выпадающем списке выберем подключённый USB Blaster. Закроем окно Hardware Setup .

В окне программатора Programmer нажмите кнопку Auto Detect , чтобы Quartus попытался автоматически определить подключённую ПЛИС и файл прошивки *.sof.

Файл прошивки создаётся Квартусом по умолчанию при компиляции и сохраняется в директории output_files , если не задано иное.

В окне Programmer выберите режим JTAG , установите галочку Program/Configure и нажмите кнопку Start . Прошивка будет записана в память ПЛИС.

в режиме Active Serial

Чтобы прошивка сохранилась в ПЗУ, запишем прошивку в режиме Active Serial .

Подключите кабель программатора к разъёму AS или Active Serial . Запустите программу прошивки: Tools Programmer .

Выберите режим Mode Active Serial . Соглашайтесь при ответе на уточняющий вопрос.

Добавим файл прошивки, нажав кнопку Add File… В поддиректории проекта output_files найдите файл с расширением .pof .

После открытия файла прошивки, установите галочки Program/Configure и, по желанию,остальные.

Обратите внимание на тип конфигурационной памяти в столбце Device : он должен соответствовать типу памяти, которая установлена у вас на плате.

Нажмите кнопку Start для загрузки прошивки в конфигурационную память ПЛИС.

Для преобразования и настройки файлов прошивок существует инструмент, который доступен из меню File Convert Programming Files… .